CAB760M12HM3 Simulation of Current Imbalance under Vths Mismatch in Synchronous Buck Topology

Dear Wolfspeed Technical Support,

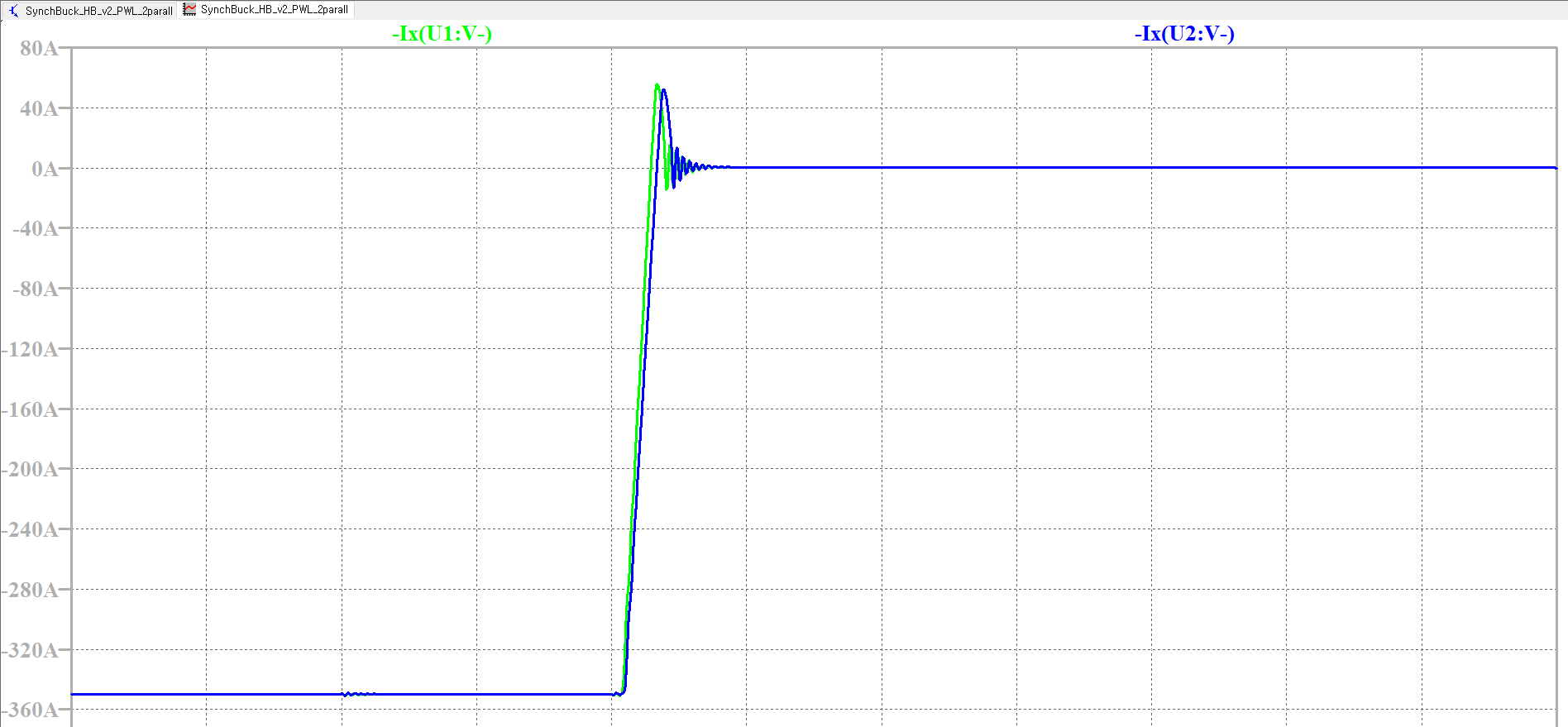

I am currently simulating the CAB760M12HM3 module in a synchronous buck converter topology, focusing on the current imbalance behavior caused by V<sub>th</sub> mismatch between two parallel high-side switches, using LTspice.

According to Infineon's application note "Paralleling Power MOSFETs in High Current Applications" (e.g., Figure 5), it is clearly observed that the turn-on timing differences caused by V<sub>GS(th)</sub> variation lead to noticeable saturation delays in the drain current of each MOSFET. Based on this, I configured the simulation with the following setup:

- Two half-bridge modules in parallel, differing only in V<sub>th</sub>

- The lower-side switch (body diode/FWD) is biased at -4V

- Both high-side MOSFETs receive the same gate signal simultaneously

However, in the synchronous buck configuration, the drain currents of the parallel devices converge too quickly, and I am unable to observe the saturation delay difference as clearly as shown in Figure 5.

I would like to ask the following:

- Are there any testbench examples or parameter configurations available that would help emphasize the current saturation delay between parallel MOSFETs in a synchronous buck converter using the CAB760M12HM3?

- When simulating with the same module in a Double Pulse Test (DPT) structure, I am able to observe a much more distinct current saturation delay between devices due to V<sub>th</sub> mismatch.

Could the lack of visible delay in the synchronous buck converter be due to the influence of the large output inductor in the converter structure? - Would it be possible to obtain a reference simulation example using CAB760M12HM3 that replicates the structure and behavior shown in Figure 5?

Although the application note attributes the effect to parasitic inductances (e.g., 1 nH, 3 nH), I have implemented similar parasitics in my simulation, but no clear delay or imbalance is observed.

Thank you very much for your time and support. Any guidance or reference material you could provide would be greatly appreciated, as it would be a significant help in validating my experiments and understanding the dynamic behavior of the module.

Sincerely,

Junhyeok

Comments

-

Thank you for your post, it has been approved and we will respond as soon as possible.

0 -

Hi Junhyeok,

While we take a closer look at your questions, please feel free to review our recently published App Note on SiC power module paralleling found here:

It contains many real-world examples of paralleling Wolfspeed SiC power modules while adjusting various parameters such as VTH, RDS-ON, and stray inductance.

Best Regards,

Austin C.

0 -

Hi, I hope that this answered your question. If it did, please click on "This question has been answered - Close Discussion" . If you have a follow up question, at a later date, please "Start a New Discussion"

0 -

Hi Junhyeok,

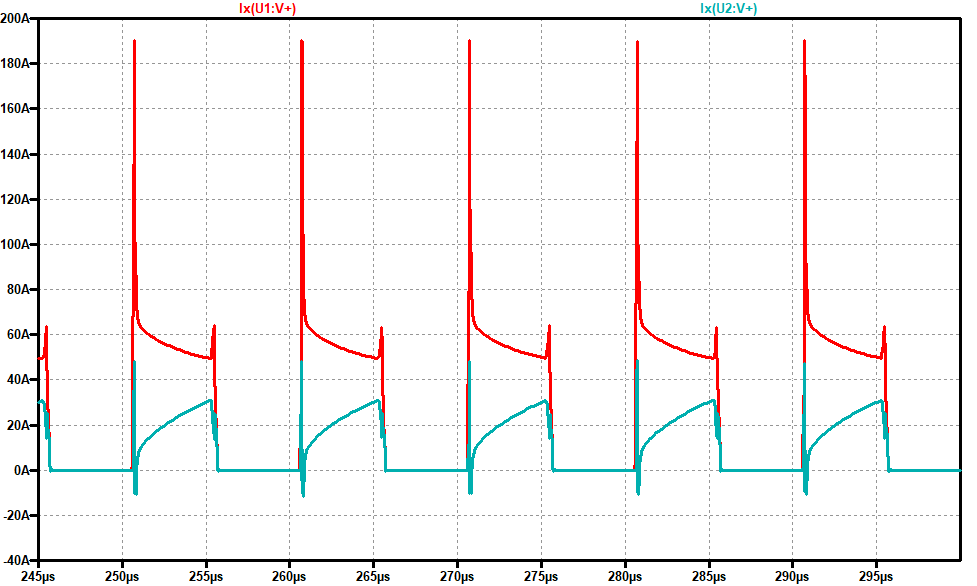

Sorry for the delay in getting back to you. I was able to observe the desired behavior in a buck converter. Please see the attached files. One important aspect here is to make sure that you have separate gate drivers for each module - the simulation struggles with oscillations if the modules are directly connected at the gate/kelvins.

Thanks,

Brian DeBoi

0

0