Unexpectedly Slow Vsd Settling Time (300-400ms) During Tj Measurement on C3M0021120K

Dear Sir or Madam,

I am currently working on a project to measure the junction temperature (Tj) of a Wolfspeed SiC MOSFET (Q1: C3M0021120K) by monitoring the forward voltage drop (Vsd) of its body diode with a pre-calibrated K-factor. However, I've encountered an unexpected and very slow Vsd settling phenomenon that I'm hoping to get some insight on.

Measurement Setup and Procedure:

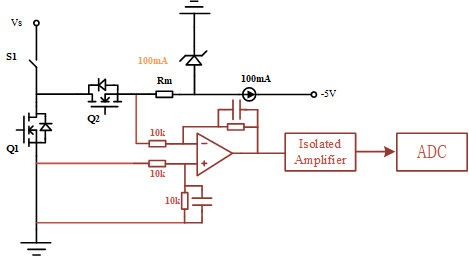

My test circuit is designed to first heat the DUT (Q1) and then quickly switch to a low-current measurement phase. The schematic is attached below.

- DUT (Q1): C3M0021120K

- Measurement Switch (Q2): IMBG120R034M2HXTMA1 (Infineon CoolSiC™)

- Sense Current: 100mA constant current source

- Vsd Measurement: A differential amplifier measures the voltage directly across the source and drain of Q1, which is then fed to an isolated amplifier and an ADC.

The measurement sequence is as follows:

- Heating Phase: Q1 is turned ON, and a DC power supply provides a constant current of 10A through its channel to heat the die.

- Transition and Measurement Phase:

- The 10A heating current is stopped, and Q1 is turned OFF.

- After a delay of 100µs, the measurement switch Q2 is turned ON, injecting the 100mA sense current through the body diode of Q1.

- After an additional 100µs delay (total of 200µs from Q1 turn-off), the ADC begins its first measurement of the Vsd.

The Problem I'm Observing:

I expected the Vsd reading to be relatively stable, reflecting the die temperature at the moment of measurement.

However, even with the 100µs settling time allowed after current injection, I am observing a very slow transient. The initial Vsd reading is significantly higher than the final value, and it takes approximately 300-400ms for this voltage to decay and settle.

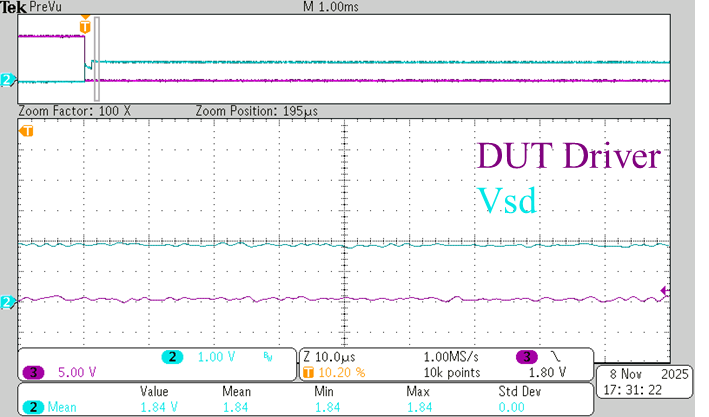

As shown in the attached oscilloscope captures:

- Capture 1 (Zoom Position: 195µs): This corresponds to the very beginning of the ADC acquisition phase. The mean Vsd is measured at 1.84V.

- Capture 2 (Zoom Position: 8.81ms): After just a few milliseconds, the mean Vsd has already dropped to 1.76V, and this downward trend continues for hundreds of milliseconds before stabilizing.

My Question:

What could be the physical mechanism behind this long (300-400ms) Vsd settling time, given that the measurement starts 100µs after the sense current has been applied?

A duration of several hundred milliseconds seems too long for a typical die-level electrical or thermal transient. Is this a known characteristic of SiC MOSFET body diodes, perhaps related to charge trapping/de-trapping or a more complex thermal effect within the package? Or could there still be an artifact from my measurement circuit that I am overlooking?

I would greatly appreciate any insights, suggestions, or similar experiences the community could share. Thank you in advance!

Comments

-

Thank you for your post, it has been approved and we will respond as soon as possible.

0 -

Greetings:

I have some questions about your circuit schematic.

- When Q1 is turned off, what voltage is applied gate to source?

- You say you are measuring VSD across Q1 but the schematic shows the differential amplifier measuring across the combination of Q1 and Q2. Can you clarify?

- If Q2 is inside the sensed voltage measurement, how much voltage (gate to source) are you gating Q2 with?

Julius R

0