Vgs static vs dynamic limit

I have been told when discussing SiC MOSFETs with other suppliers that the difference between Vgs max and Vgs Max recommended is to allow for overshoots in Vgs voltage when switching. Is this also the case with Vgs static vs dynamic? Can we apply a higher voltage than Vgs static, but lower than Vgs dynamic, if we have no overshoots?

Comments

-

Hi Lukas - thank you for posting. Your understanding of Vgs Max and Vgs max recommended is correct. Before I answer your second question, I would like to know which datasheet you are referring to in the second part of your question. This will allow us to give you a more qualified answer.

Thank you

0 -

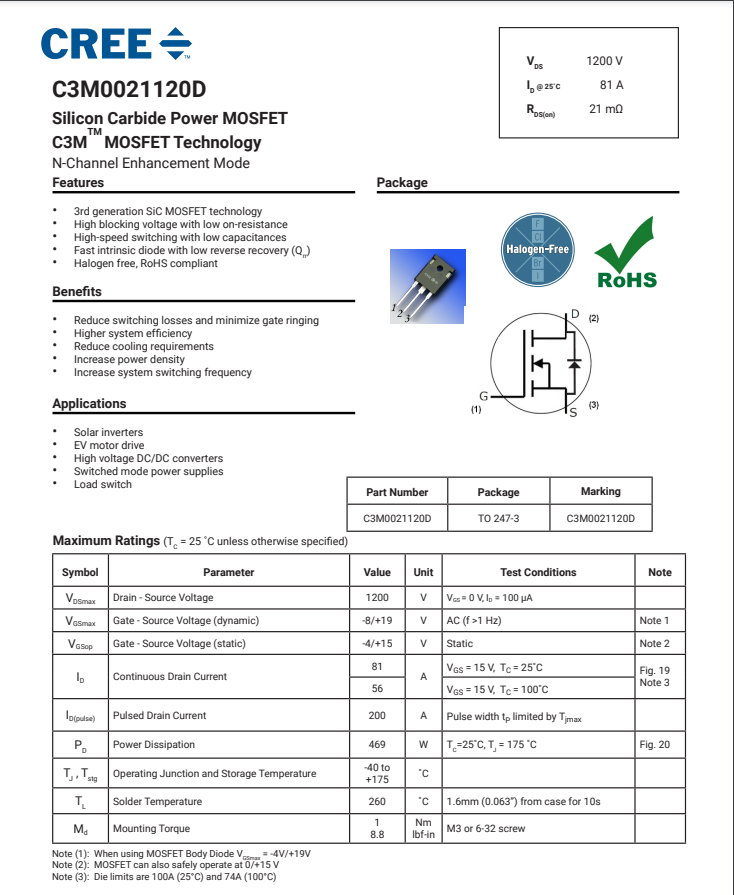

For this MOSFET (C3M0021120D) can we use a gate voltage supply of 16V instead of 15V if we guarantee no overshoots when switching the MOSFET on?

0 -

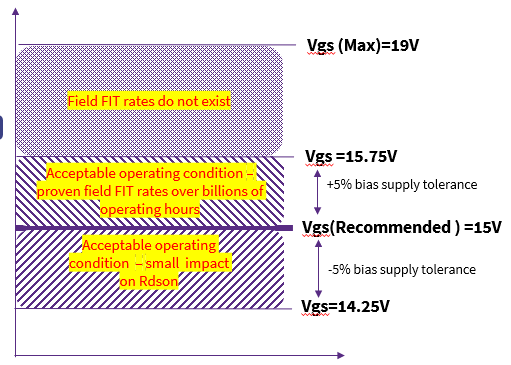

Hi Lukas - thank you for the image. The image below should explain the spec a little more clearly. Essentially, we expect that bias supply designs will have a +/-5% tolerance for inaccuracy around the Vgs(Recommended/static) value and hence our historical known FIT rates (customer use in the field) are based on that usage condition and tolerance. No historical field FIT data exists beyond 15V + 5% and hence we would not recommend that a Vgs(Static) be set beyond that. Please let us know if this explanation is clear.

0 -

Yes this explains it clearly! We will aim for a design that has supply voltage at 15V since we are looking for a low RdsOn in our application.

0