Vertical Mounting TO-247 - 4L C3M0032120K

Noticed in your training presentation for this part application 22kw AFE that you set the vertically mounted FET to the notch in pin 1. Our application has them mounted without bent legs. Min inductance of course is the goal. Is this a best practice for these devices? What is the purpose of this notch in you device? (not all devices have this notch).

Comments

-

Hello Ralph,

Thank you. It is a good question. In Wolfspeed 22kW AFE, a baseplate is applied for cooling. So we bent the leads to mount the devices. If you can mount the devices on your heatsink without bent leads, that is very good since you got the min inductance. For the notch on the device, that is designed for larger creepage. The required creepage between drain and source depends on the voltage stress and contamination level in your application. A larger creepage can reduce the risk of arcing between leads if there is dust, pollen or other contamination. Remember to add a PCB slot between drain and source if you would like to keep a larger creepage.

I hope this answers your questions. if you have further question, please don't hesitate to ask.

if this question has been answered, please help to close the discussion. Thank you

Regards,

Frank Wei

0 -

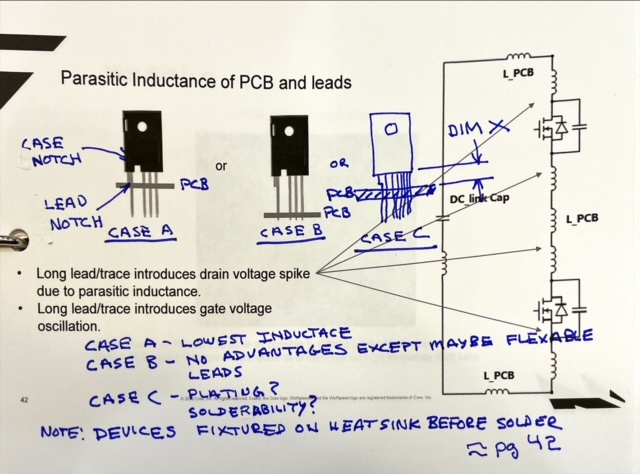

I am sorry for not making my question clear let me try again. First I am talking about the notch in pin 1 not the notch in the case. I would like to keep inductance as low as possible and was wondering about the best practices revolving around Dim X, mainly do I set the FETs to the Lead Notch in pin 1 or fixture to a specific Dim X. Hopefully the attached picture will help.

Ralph

0 -

Hello Ralph,

Thank you for your further inputs. Got your point, you would like to modify the device and remove the stand-offs in your Case C. Do you want to make 1 or 2 lab units or mass production?

if you just need to prepare some lab units by manual soldering to show the performance, you can try to cut the leads do that in your lab.

But if it is designed for mass production, Case A is recommended. Rather than the paracitic inductance, you also need to consider the mechnical stress on the device, the thermal stress on the moulding compand during wave-soldering and the thermal stress on the PCB/ soldering joint during operation. If the loop inductance is really very critical in your design, you can also try to use SMD devices.

I hope this answers your questions. if you have further question, please don't hesitate to ask.

if this question has been answered, please help to close the discussion. Thank you

Regards,

Frank Wei

0 -

First, our production inverter runs are normally run between 100 and 1000 units. Specialty products.

I don't understand your comments about removing standoffs. What? Lead trimming? Removing or modifying notch? Anyway let me try again.....

I reread you answer to my question regarding your training presentation and the best practices regarding vertically mounting FETS for low component lead inductance. Let me try asking my questions as a series of multiple-choice questions.

Q1) What is the purpose of the notch in Pin 1? Not all similar FETs have this notch. You added for a reason I am not familiar with.

a) Provides min height (Dim X) for locating the FET with respect to the PCB.

b) Provides additional cooling, protection for the Drain.

c) Is a fixturing feature for internal manufacturing.

Q2) What View on my mark up View A or B or C best reflects the best practice for vertical mounting your FET.

a) View A as in the presentation with the top of the notch resting on the PCB

b) View B with a longer lead length either bent or straight.

c) View C set to specific standoff Dim X either by tooling or a specific FET Standoff

d) Other

Q3) What do you think is a good dimension for Dim X?

a) 0 like in presentation, View A, you will just have to avoid stress on the lead

b) 5 mm, it is hard to avoid stressing the lead as shown in presentation

c) 6.4 mm, this should be a good compromise between with low inductance, ease of soldering and joint integrity

d) Other

Thanks for your help

0 -

Hi Ralph,

Sorry. I misunderstood your previous question.

Please see my answers here.

Q1) What is the purpose of the notch in Pin 1? Not all similar FETs have this notch. You added for a reason I am not familiar with.

a) Provides min height (Dim X) for locating the FET with respect to the PCB.

Q2) What View on my mark up View A or B or C best reflects the best practice for vertical mounting your FET.

a) View A as in the presentation with the top of the notch resting on the PCB if you want minimun inductance.

c) View C set to specific standoff Dim X either by tooling or a specific FET Standoff if you have fixed multiple devices on the heatsink before soldering. you also solder the lead of your heatsink on the PCB to fix the assembly, right? Considering the tolerance of the notch on Pin 1 and Pin 4, you can use a fixture to set a Dim X. to mimimize the inductance, the Dim X can be the maximun length of the notch on Pin 1 and Pin 4 considering tolerance. the notch on the Pin 4 was not shown in the presentation.

Q3) What do you think is a good dimension for Dim X?

a) 0 like in presentation, View A, you will just have to avoid stress on the lead. --> Quite a few customers did in this way. Please try to fix your heatsink on the PCB. don't rely on the leads of the MOSFETs to fix the heatsink on PCB.

d) Other to mimimize the inductance, the Dim X can be the maximun length of the notch on Pin 1 and Pin 4 considering tolerance. the notch on the Pin 4 was not shown in the presentation.

if you have further question, please don't hesitate to ask. thank you

Regards,

Frank

0 -

Thanks for your help

0