CRD25DA12N-FMC power loop inductance

Hi, there are only 3 x 65 uF capacitors are present and no high frequency capacitors are used in the DC-Link of this design. DC+ and DC- is interleaved across 4 layers. Can you share the power loop inductance of this design?

Comments

-

Thank you for your post, it has been approved and we will respond as soon as possible.

0 -

Hello jiten000,

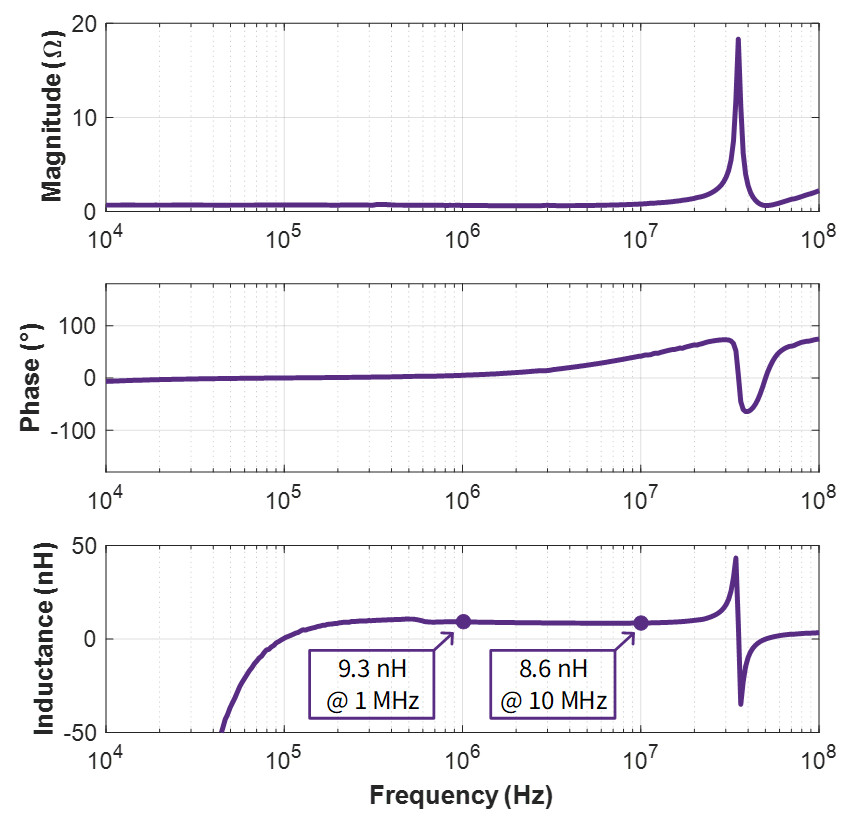

Thank you for your question. The power loop inductance was measured to be 8.6 nH at 10 MHz. The measurement results are provided below.

Thanks,

Chris N.

0 -

Hi Chris,

Thanks for your reply. What is the overshoot observed on Drain?

Regards,

Jitendra

0 -

Hello Jitendra,

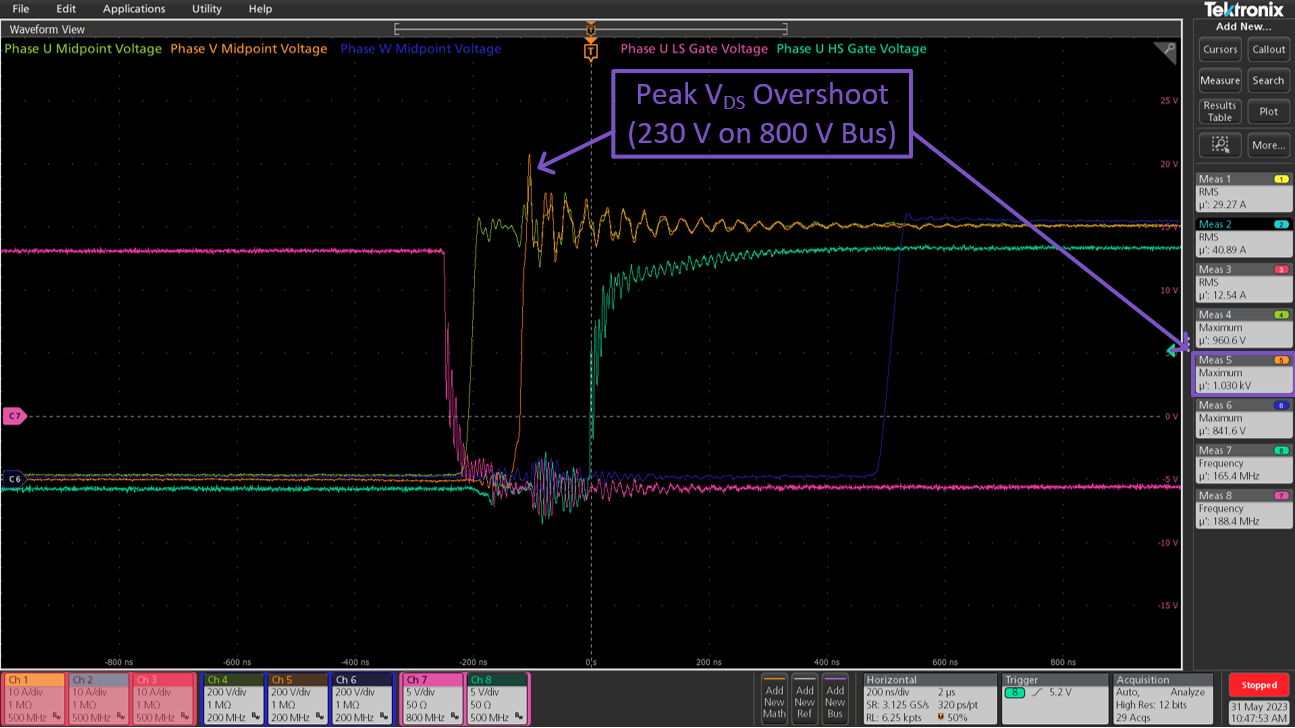

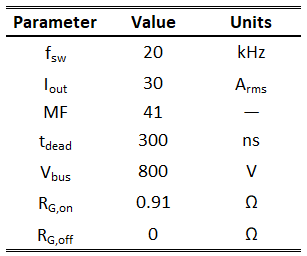

Thank you for your follow-up question. Below is a oscilloscope screenshot from one of our experimental tests. The maximum observed VDS in our testing was 1.03 kV (230 V of overshoot on 800 V bus), which is well within the safe operating region of the power module. The operating conditions for this experiment are summarized in the table below. If necessary, this overshoot can be reduced by increasing the gate resistances.

Thanks,

Chris N.

0 -

Thanks

0