Spice Wolfspeed Models

Hello all,

I am trying to create a model of my 3 phase inverter system in order to investigate in more details several (mostly EMI related) issues that are arising. At the same time I am referring to the following documents provided by Wolfspeed:

- Wolfspeed Power Module SPICE Models User Guide

- Power Module Baseplate Capacitance and Electromagnetic Compatibility

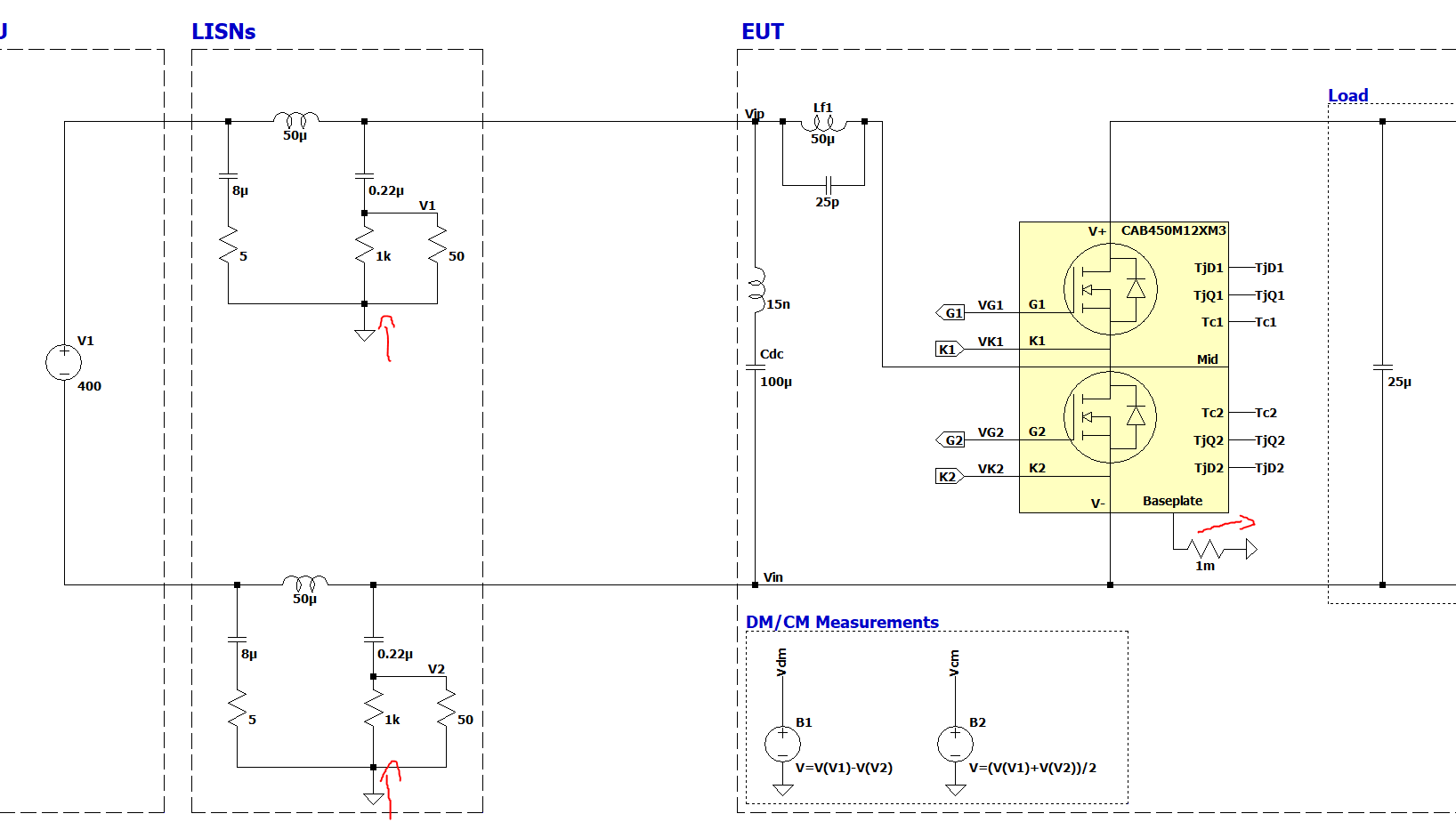

The inverter has 3 CAB450M12XM3 power modules, but for the current model that I am using, I have only included one module.

At the same time, I am using the ADuM4135 gate drivers to drive this module. I did this since the ICs on the gate drivers that come with said modules are exactly these.

Apart from that, in order to really be able to capture all the effects that result in this EMI/noise issues, I have tried to include the parasitic components of the system. These are listed below:

- DC-Link Bank

C = 330u

ESL = 4.3n

ESR = 0.4m

This capacitor bank consists of 3 Capacitors connected in parallel. - Parasitic loop inductance

LLoop = 10n

This is the approximate inductance that I am measuring across the DC Busbar, which stands between the HV Battery input and Module DCIN tab. - Parasitic Output inductance.

Lbbar = 100nF

This is the approximate inductance I am measuring across the busbar that stands between the phase output tab of the module and the motor phase terminal. - Baseplate to (LV)GND/Chassis Resistance

RBPC1 = 100m

This is the resistance I am measuring between the baseplate of the module and the casing of the inverter.

My objective is to first create such a model that it replicates the results I am getting with my prototype during testing.

The second step would be to include a model of a common mode filtering (and Y capacitors) and see how would the system improve as a result of this addition.

And so, having given this information, I have the following questions and concerns.

- Is my approach, in terms of inclusion and modelling of the parasitic components, correct? Are there any other parasitic components that I should include in my model in order to have the system resemble more to the one in reality?

- Is there an available model of the System shown in figure 27 of the following document: "Power Module Baseplate Capacitance and Electromagnetic Compatibility"?

- What does the {Rshunt} resistor on the Wolfpseed Spice Example models represent?

- Following the instructions on the Wolfspeed documents, if I right clock on the symbol of the module that I am using I should be able to open the symbol and bring up the attributes editor.

If I try to do this however, the only window that comes up is the one shown in the figure.

I am fairly certain that I will have other questions related to this task, but if I could get an answer or help on these issues, that would already be helpful.

Thank you in advance,

Konstandin Kotsis

Comments

-

Thank you for your post, it has been approved and we will respond as soon as possible.

0 -

Hello,

I'm happy to help answer some of your questions.

- It's a good start. One of the challenges with simulating EMI is that you often don't know where parasitic coupling will exist. These coupling paths can often be quite unexpected, especially when common-mode current is involved. Also make sure you consider if the any equipment (oscilloscopes, spectrum analyzers, power supplies, etc) are involved in the emissions path. A nice feature of simulation is that, once your system is set up, you can add parasitic couplings around the circuit to try to match what you are seeing empirically and use that information to improve your circuit.

- I've included a version of that circuit here you can get started with.

- The 'Rshunt' resistor is the current viewing resistor that we commonly use to measure current on our evaluation boards. See PRD-08333 for more information on this.

- Try using ctrl+right-click. The LTspice GUI was updated recently and this is one of the changes that they made.

Please let me know if you have any further questions.

0 -

Hello,

Thank you very much for your feedback.

I have been looking into the booster model, and try to use it as a reference for my model.At first sight and simulation of the booster model, the following questions and concerns came to mind:

- I tried to remove the CM+DM Mode filter in order to bring the circuit to its initial state before resolving the noise issues, and compare it to the results shown in the wolfspeed document: Power Module Baseplate Capacitance & Electromagnetic Compatibility.

One thing that I notice when measuring the current through the baseplate resistor (1m) is that the amplitude of this current does not correspond to what I am reading in the document. In the document the amplitude is about 10A peak-to-peak before it starts attenuating, meanwhile on the booster model it is only about 450mA peak-to-peak before it starts attenuating.

The waveform does look similar however I do not understand where is this mismatch coming from.

Also doing a rough calculation (although I am also not sure if this is the right way to do it, so correct me if I am wrong) and assuming a BPC = 382.5pF (Cug+Cag+Clg); a rise time of 10ns as stated in the Gate Drive parameters and a dV of 400V, then you would expect a leakage current of:

C*(dV/dt) = 382pF*(400V/10nS) = 15.28A, which although high, seems to be closer to the value shown in the document.

- Trying to look into the emissions of my system, the same way as they do on the Wolfspeed document above mentioned, I cannot seem to be able to express my emissions as [dBuV]. Is there a way to do this on LTspice?

- Compering the booster model to my model, I noticed the following:

Although I was using the same gate drivers that I have installed on the actual prototype, the rise time that I would measure on the model did not really match with the rise time that I measured in real life.

That is why I have substituted to whole gate driver system and components to a generalized one using voltage sources, where I define the rise and fall times myself. This resulted in a rise time which is much closer to what I am measuring on the actual prototype.

There is however one more mismatch: At a requested output current of 5A, the overshoot that I have measured between one of the output phases and HVDC- was close to 100V before starting to attenuate. On my model this overshoot is about 20V only. I have included a parasitic loop inductance that I have measured (10nH).

Does this mean that my system has more parasitic coupling that I am aware of?

Is this only related to the parasitic loop inductance between the DC-Link capacitors and the high-side switch or are there also other parasitics that I might have to consider?

Is there a way to include the parasitic capacitances Cgd, Cds, and Cgs in "SpiceLine2" same as I have done for Cug, Cag, and Clg? Would that work?Finally, measuring a leakage current through the Baseplate resistance I measure an amplitude of about 40uA which again seems quite small considering a BPC = 434pF; dv/dt = 800/80ns (calculations done similarly to what I have explained on my first question). I would expect a leakage current of around 4A.

Thank you very much in advance.

Looking forward to hearing from you.Best regards,

Konstandin0 - I tried to remove the CM+DM Mode filter in order to bring the circuit to its initial state before resolving the noise issues, and compare it to the results shown in the wolfspeed document: Power Module Baseplate Capacitance & Electromagnetic Compatibility.

-

Hello,

I was able to recreate the circuit and match what was in the document. Keep in mind that the module in the document is a BM3, whereas you are using an XM3, so I don't expect them to match perfectly.

To convert from dBV to dBuV, simply add +120 to your data (note: you can't do this in the FFT in LTspice, the +120 was added after exporting the data for the document). So, 0 dBV converts to 120 dBuV, -50 dBV converts to 70 dBuV, and so on.

After looking over your sim where you are getting the uA baseplate current, remember that the baseplate capacitance provides a path for common-mode current to flow. However, if you look at your circuit, you have the baseplate connected to a ground that goes to nowhere. In the Wolfspeed document, the simulation includes line impedance stabilization networks (LISNs). You'll notice that these LISNs are connected to ground. This provides a path for the current to flow in/out of the baseplate, up through the LISNs, and into the rest of the circuit. Current flows in loops, so you need to think about what your baseplate is attached to in your system and how that current might couple into more sensitive electronics. If it's common-mode current, it can flow in very unintuitive ways. The baseplate capacitance is also not the only source of EMI — any parasitic couplings in your system can provide a path for emissions to flow. If you have more details on your system or what kind of EMI issues you are experiencing, I can try to point you in the right direction.

Your idea of replacing the MOSFETs with voltage sources with an edge rate that matches your empirical setup is a very good one - this is commonly done to make equivalent models that can be solved analytically.

As for the voltage overshoot, there could be several causes. One would be if the di/dt of the switching in the simulation does not match your empirical setup. The second would be if you are missing parasitic inductance in your system. It's hard to tell which is the case without more information.

You can't set the exact capacitance for cgs/cgd/cds in your sim, as those are not static capacitances but vary with voltage. However, there are scalar parameters available that you can adjust below. Note: these values may not be equal to 1 by default in the model

Rgis - scales the internal gate resistance.

ags - scales the gate-source capacitance

agd - scales the gate-drain capacitance

ads - scales the drain-source capacitance

If you have access to academic articles, here are some you may be interested in to better understand EMI, common-mode paths, and how these relate to baseplate capacitance. This topic does get complicated, though.

1

1 -

I hope that this answered your question. I will close this discussion for now but if you have a follow up question, please "Start a New Discussion" and we would be glad to support you further.

Blake

0